# **TDR Pattern Register User Manual**

#### Contents

- 1. Introduction.

- 2. Function.

- a. Block Diagram.

- b. VME interface specification.

- c. SHARC interface data format.

- 3. Setting up.

- a. VME Address Jumpers

- b. Input selection.

- 4. Operation

- a. Single input mode

- b. Gated Group

- c. GroupA AND GroupB.

- 5. Software Interface.

- 6. Front Panel Interface.

- 7. Logic Inspection Signal examples.

- 8. What can stop the module working, or Error management.

#### Appendices

- A. Layout of the PCB with Jumper locations.

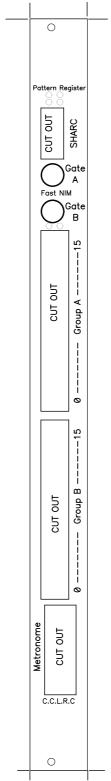

- B. Front Panel Layout.

- C. MIDAS control window.

Refers to pcb 25/9275A.

# 1. Introduction

The Pattern Register is a single w idth VME module designed to operate in the GREAT TDR environment. There are two groups of 16 inputs, A and B. The purpose of the module is to regist er the changes on the inputs, and send a timestamped 16 bit pattern to the Data Acquisition system via a SHARC link. The timestamp refers to the selected edge of the input. The two groups can be set to one of three specific digital interface types. Fast NIM, Differential ECL, and Single ended ECL.

The Pattern input is operated as two Groups, each in one of three operating m odes. All the pattern inputs are AND' ed with a programm able m ask bit, which allows individual bits to be disabled, for exam ple where one input is firing in noise. GroupA can be pulse stretched under computer control.

1. Gated Group:

The front edge of the Gr oup Gate input will latch the master 100MHz counter and all inputs which are active at any time during the Group Gate will be included in the pattern. The pattern and timestamp is output at the end of the Gate.

2. Individual inputs:

- a) The 16 pattern inputs of the Gr oup are individually sam pled on every clock. Thos e that becam e active s ince the previous clock generate a timestamp along with a label to say wh ich of the 16 i nputs caused the timestamp.

- b) In this m ode the user m ay choose (under com puter control) to AND the input with the Group Gate.

- c) GroupA AND GroupB. This mode uses the GroupA and GroupB inputs to provide 16 bits of co-incidence pattern. A timestamp is generated when the input from GroupA AND GroupB are true to-gether.

The Ti mestamp is based on a counter increm ented by a 100Mhz clock and kept in synchronism with the rest of the T DR system by the SYNC pulse provided by the GREAT TDR system Metronome module.

The Pattern Register is designed to operate at an average input rate of 10Khz per input. The maximum burst rate into one input is 10Mhz. The minimum input pulse width for reliable operation is 50ns, howev er m uch s maller input pulses can be registered.

The following docum ents will h elp in unders tanding the term s discussed in th is manual. They can be found at the Nuclear Physics Group web site : <u>http://npg.dl.ac.uk</u>

EDOC502 The GREAT Triggerless Total Data Readout Method (IEEE TNS, VOL. 48, NO. 3, JUNE 2001) EDOC503 The GREAT 32 Channel Peak Sensing ADC : User Manual EDOC504 The GREAT data format. EDOC507 The GREAT TDR system Error recovery, and experiment timing EDOC511 Metronome User Manual Version6 (C1100)

# 2. Function

The function of the module is carried out by two Altera FPGA devices programmed at power-up from serial EPROMs. There is an LED for each FPGA which is lit when the programming has completed successfully.

The user of the module must decide the interface type for each of the 16 inputs in the two Groups. The jum pers must then be set accordingly. Refer to section 3.b and appendix A for setting the different interface choices.

The inputs to be reg istered are chosen by using the MIDAS interface window. See appendix C for an example of the window for the Pattern Register.

The sense of each input can be inverted, controlled via MIDAS, prior to being applied to the Register timestamp logic. This allows the user to decide which edge of the input signal causes the tim estamp. It is always the rising edge of the input that is timestamped.

As mentioned in the introduction each group operates in one of two modes. The mode must be selected via the MIDAS interface.

To operate the module must be connected to a TDR Metronom e output, or a similar source of 100Mhz, and SYNC pulses.

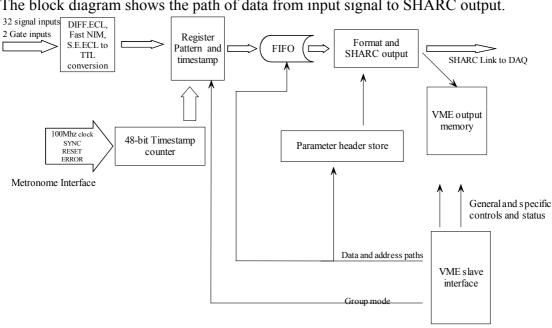

# a. Block Diagram

The block diagram shows the path of data from input signal to SHARC output.

**GREAT** Pattern Register P.J.Coleman-Smith

# b. VME interface specification

The Pattern Register is an A32/D3 2 slave. The interface will respond to acces ses made using D16, and D08, however they will not return the correct values. The Pattern Register o ccupies 2<sup>16</sup> bytes in A32 m emory space. T he address of

location 0 is specified by jum pers set on the pcb. See section 3.a and appendix A for setting the address base.

### c. SHARC interface data format.

The Pattern Register outputs two 32 bit words for every Item. An Item can be for an input transition from Gr oupA, or GroupB, a SY NC pulse, a flow control Pause, or a flow control Resum e. Refer to E DOC504 for m ore inform ation about the bit allocation of these two words.

Here is an outline of the Item format extracted from the EDOC.

#### **Group Pattern Data format**

| 31 | 30       | 29 | 28 | 27 to 16                        | 15 to 0  |

|----|----------|----|----|---------------------------------|----------|

| 1  | 1        | 0  | 0  | Data Source Ident, Pattern data |          |

|    | 31 to 28 |    |    | 27 to 0                         |          |

|    |          | 0  |    | Time Sta                        | amp 27:0 |

#### **Other Information.**

| 31 | 30       | 29 to 24      |  | 23 to 20    | 19 to 0           |

|----|----------|---------------|--|-------------|-------------------|

| 1  | 0        | Module Number |  | Information | Information Field |

|    |          |               |  | Code        |                   |

|    | 31 to 28 |               |  |             | 27 to 0           |

|    | 0        |               |  | Tim         | e Stamp 27:0      |

The Module number identifies the source of the information.

| The information codes used in the Pattern Register are as follows. |      |                              |  |  |

|--------------------------------------------------------------------|------|------------------------------|--|--|

| Information Type                                                   | Code | Information Field Definition |  |  |

| Undefined Data                                                     | 0    |                              |  |  |

| Pause Timestamp                                                    | 2    | Timestamp bits 47 : 28       |  |  |

| Resume Timestamp                                                   | 3    | Timestamp bits 47 : 28       |  |  |

| SYNC100 Timestamp                                                  | 4    | Timestamp bits 47 : 28       |  |  |

The Information codes used in the Pattern Register are as follows:

# 3. Setting Up

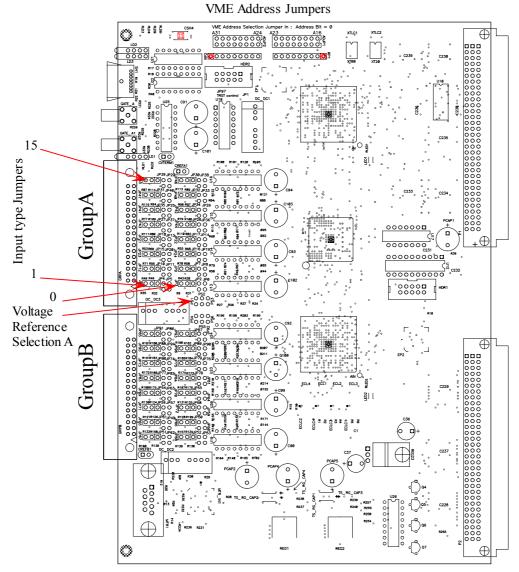

#### a. VME Address Jumpers.

Refer to the picture of the m odule shown in Appendix A. The VME address jum pers are in two, eight jum per blocks at the middle of the top of the pcb. The address of location 0 of the module address space is specified by placing, or not, shorting links ion the jum pers. Placing a shorting link on a jumper will select that address bit to be seen as a logic 0.

For example to select address 0x80000000 for the base address, shorting links should be placed on every jumper except the one for A31. (This is the jumper at the left most end of the row, as indicated by the white writing ).

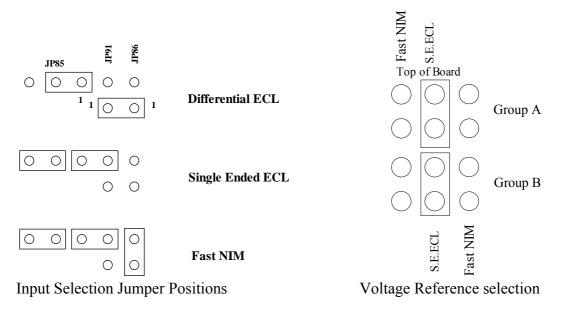

#### b. Input Selection

Each of the 32 inputs can be selected to interface to signals of one of three types. Fast NIM, Differential ECL, and Single ended ECL. The following jumper diagrams show how to select each of the possible types.

Differential ECL does not require a specific reference voltage selected, but the Fas t NIM, and Single Ended ECL do.

It is important to note that all the inputs for a group should be set to the same interface type. Failu re to do this will result in incorrect reference voltages being used, and unpredictable register operation ;-)

When connecting to the front panel inputs use the following signal allocations with the 34 pin IDC connectors.

Input 0 in <u>*Differential ECL*</u> mode pin1 is the +ve input, and pin 2 the –ve. This carries on through the connector with Input 15 on pin 31 for +ve and pin 32 for –ve. Pins 33, and 34 are not connected on both Group A and B input connectors.

Input 0 in *Fast NIM*, and *Single Ended ECL* mode pin1 is the Signal input, and pin 2 the GND. This carries on through the conne ctor with Input 15 on pin 31 for Signal input and pin 32 for GND. Pins 33, and 34 are not connected on both Group A and B input connectors.

# 4. Operation

The mode of operation applies to all the inputs of a Group. The mode is selected using the MIDAS interface.

The operation of the module is handled by the MIDAS interface, and would norm ally only require the user to select the inputs, their polarity, and the Group Modes. If the module is to be operated in an environm ent not controlled by MIDAS, then a m uch deeper understanding of the m odule function is required than is covered in this version of the user manual. Contact the author for help.

To operate within the MIDAS environment the module must be configured in the VME address space, and the correct Group In terface jumper settings selected for the inputs. The module is entered in the VME configuration table accessed via the VME control window. This allows the MIDAS to set-up and control the module.

With the SHARC link connected to the TDR Collator processor, and the Me tronome interface connected the module will be set-up by the MIDAS with initial values in all the registers, and valid entries for the module readout identifiers.

Use the Experiment Control window Setup and Go buttons.

The mode of operation of the two groups of inputs is controlled by m enu selection in the MIDAS interface. The tab le below gives the valid m odes. A# refers to the input number within the group A.

| Value | Mode name                              | Comment            |  |

|-------|----------------------------------------|--------------------|--|

| 0     | Single: input(A/B)# AND Gate(A/B)      |                    |  |

| 1     | Single: input(A/B)#                    |                    |  |

| 2     | Gated Group                            |                    |  |

| 4     | Single : A# AND B# AND GateA           | Group A input only |  |

| 5     | Single : A# AND B# Group A input on    |                    |  |

| 6     | Gated Group : A# AND B#                | Group A input only |  |

| 12    | Single : Stretched A# AND B# AND GateA | Group A input only |  |

| 13    | Single : Stretched A# AND B#           | Group A input only |  |

#### a. Single Input mode.

In this mode each input operates alone. E ach input must be enabled via the MIDAS interface. The Group Gate input can be selected to be AN Ded with the inputs. This selection operates for the whole of a group.

#### b. Gated Group.

The front edge of the Group Gate in put will latch the master 100MHz counter and all inputs which are active at any time during the Group Gate will be in cluded in the pattern. The Group Gate input is a Fast NIM signal.

# c. GroupA AND GroupB, or Using the TDR Pattern Register for providing timed suppression data.

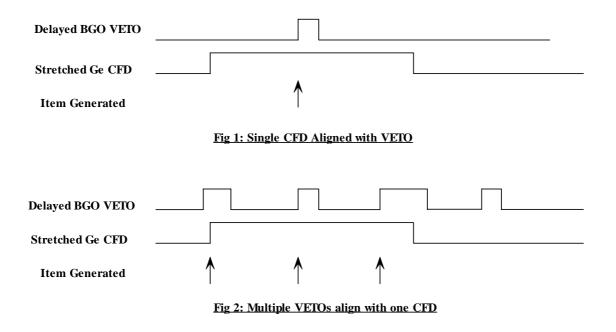

The purpos e is to combine the VETO signal from the Eurogam Phase 1 BGO detectors and electronics with a Ge CFD to give a timestamped data item indicating the co-incidence of the two signals.

The Pattern Register 32 inputs are allocated as two groups of 16. Group B is used for the Single Ended ECL VETO signals from the BGO electronics, and Group A is used for the Fast NIM Ge CFDs from the LeCroy CFD modules.

The Ge CFD signals a re str etched in the Pattern Registe r to align the m with the slower VETO signals. Fig 1 shows when the timestamped Item is generated for a single CFD and VETO.

It should be noted that a timestamped Item will be gene rated for <u>every</u> coincidence between the VETO, and CFD. Fig 2 show s how this can occur during m ultiple VETOs

When setting up for an experim ent it will be necessary to check the alignment of the Ge CFD and VETO signals, as well as the width of the CFD.

Logic Inspection Lines are provided in each Pattern Register for this job.

The width of the CFD output pulse will also affect the number of co-incidences.

#### 5. Software Interface

Access to the registers on the Pattern Re gister are via the V ME bus interface using A32/D32 commands. The register s are defined in the table in Appendix E at the end of this docum ent. For further information about register function contact the author via email.

The normal method of control is via the MIDAS control window. The module should be initialized after power-up with registers set as follows.

# 6. Front Panel Interface

The front panel layout is shown in a diagram in Appendix B. The connections are detailed in the following Tables.

| Pin | Function    | Source           |

|-----|-------------|------------------|

| 1   | Clock       | Pattern Register |

| 2   | Acknowledge | VME Processor    |

| 3   | GND         |                  |

| 4   | Data 0      | Pattern Register |

| 5   | Data 1      | Pattern Register |

| 6   | Data 2      | Pattern Register |

| 7   | Data 3      | Pattern Register |

| 8   | GND         |                  |

| Pin | Function      | Pin | Function      |

|-----|---------------|-----|---------------|

| 1   | Input 0 +ve   | 2   | Input 0 -ve   |

| 3   | Input 1 +ve   | 4   | Input 1 –ve   |

|     |               |     |               |

| 31  | Input 15 +ve  | 31  | Input 15 –ve  |

| 33  | No Connection | 34  | No Connection |

#### Group Inputs (A/B) Differential ECL Interface

Group Inputs (A/B) Single Ended ECL Interface

| Pin | Function      | Pin | Function      |

|-----|---------------|-----|---------------|

| 1   | Input 0       | 2   | Ground        |

| 3   | Input 1       | 4   | Ground        |

|     |               |     |               |

| 31  | Input 15      | 31  | Ground        |

| 33  | No Connection | 34  | No Connection |

Group Inputs (A/B) Fast NIM Interface

| Pin | Function      | Pin | Function      |

|-----|---------------|-----|---------------|

| 1   | Input 0       | 2   | Ground        |

| 3   | Input 1       | 4   | Ground        |

|     |               |     |               |

| 31  | Input 15      | 31  | Ground        |

| 33  | No Connection | 34  | No Connection |

# 7. Logic Inspection Signal examples

During normal use of the module the inputs, and Gate signals are the most likely to be required. The examples show which edge of the signal as seen through the Inspection Lines generates the Timestamp.

# 8. What can stop the module working, or Error management.

1. Lost Track.

Refer to the block diagram in section 2.a. There is a FIFO between the timestamping input stage, and the formatting and SHARC link stage. The data is placed into the FIFO with a four bit count to keep track of the data through the FIFO. If the data coming through the FIFO is not in step, then the module will stop working, the Lost Track LED will light, and the relevant bit is set in the status register. The operation of the module is restarted by a system STOP/SETUP/GO action.

2. Using the wrong edge of the input for timing.

#### 3. Appendix A Jumper Layout

Outline of the Pattern Register for location of Jumpers.

### **Appendix B Front Panel Layout**

Front Panel for 25/9275 All Dimensions in mm All hole sizes are for finished size.

#### Appendix C MIDAS control window.

# Appendix D Logic Inspection signal examples.

# Appendix E Software Register definitions.

Register definitions:

| Address offset<br>Hexadecimal | Name                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                             | Module Control             | <ul> <li>0 : ignore track. 1= Ignore the tracking data when reading FIFO</li> <li>1 : SHARC enable. 1 = Enable SHARC link readout of the FIFO.</li> <li>2 : Reset FIFO</li> <li>3 : STARX enable. 1= Enable STARX to reset FIFO.</li> <li>4 : Soft Reset input chip.</li> <li>5 =&gt; 15 : registered data, but no action.</li> <li>16 =&gt; 31 : always return 0.</li> </ul>                                                                                |

| 4                             | Module Status              | 0 : interrupt.<br>1 : lost track.<br>2 : FIFO Half full.<br>3 => 31 : Always return 0.                                                                                                                                                                                                                                                                                                                                                                       |

| 8                             | Interrupt Control          | 0 => 7 : Interrupt vector.<br>8 => 10: Select IRQ line to drive on VME bus.<br>11 => 15 : registered data, but no action.<br>16 => 31 : always return 0.                                                                                                                                                                                                                                                                                                     |

| С                             | Interrupt Select           | <ul> <li>0 =&gt; 3 : Select Interrupt source.</li> <li>0: Lost Track.</li> <li>1: FIFO half full.</li> <li>2 =&gt; 15 not defined.</li> <li>4: Method. 0 = Edge triggered, 1 = Level Triggered</li> <li>5: Edge. 0 = Rising edge, 1 = falling edge.</li> <li>6: Level. 0 = High Level, 1 = Low level.</li> <li>7: Enable 0 = Disabled, 1 = Enabled.</li> <li>8 =&gt; 15 : registered data, but no action.</li> <li>16 =&gt; 31 : always return 0.</li> </ul> |

| 10                            | Read FIFO                  | $0 \Rightarrow 31$ : FIFO output data.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14                            | Read Tracking<br>Registers | 0 => 3 : Readout track Counter<br>4 => 7 : Track number from FIFO.<br>8 => 11 : ID track number from last ID word.<br>12 => 15 : Track number from last Time stamp.<br>16 => 31: 0.                                                                                                                                                                                                                                                                          |

| 18                            | FIFO Flags                 | All these flags are active low.0 : Almost full.7 spaces remaining.1 : Almost empty.7 words written.2 : Half full.131,072 words written3 : Empty.262,144 words written5 => 31 : 0.                                                                                                                                                                                                                                                                            |

| 1C                            | Spare Bus                  | 0 => 31 : VME chip end of Spare connections between the two Alteras                                                                                                                                                                                                                                                                                                                                                                                          |

| 100                           | Group A input<br>enable    | Bits $15 \Rightarrow 0$ enable an input when set.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 104   | Group A Invert                | Bits $15 \Rightarrow 0$ invert the logic of the input bit when set.                  |  |  |

|-------|-------------------------------|--------------------------------------------------------------------------------------|--|--|

| 108   | Group A mode                  | Selects registered/free/free & Gate mode.                                            |  |  |

|       | _                             | 0: Free Transition Mode. 1= enabled.                                                 |  |  |

|       |                               | 1: Registered Mode. $1 = $ enabled.                                                  |  |  |

|       |                               | 2: AND mode (CFD + VETO) 1= enabled.                                                 |  |  |

|       |                               | 3: Stretch input pulses. $1 = enabled$ .                                             |  |  |

| 110   | Group A Stretch<br>value      | Bits $3 \Rightarrow 0$ select the pulse stretch value in steps of 50ns.              |  |  |

| 200   | Group B input                 | Bits $15 \Rightarrow 0$ enable an input when set.                                    |  |  |

|       | enable                        | 1                                                                                    |  |  |

| 204   | Group B Invert                | Bits $15 \Rightarrow 0$ invert the logic of the input bit when set.                  |  |  |

| 208   | Group B mode                  | Selects registered/free/free & Gate mode.                                            |  |  |

| 300   | Inspection Line 0             | Selects the signal source                                                            |  |  |

| 304   | Inspection Line 1             | Selects the signal source                                                            |  |  |

| 308   | Inspection Line 2             | Selects the signal source                                                            |  |  |

| 30C   | Inspection Line 3             | Selects the signal source                                                            |  |  |

| 300   |                               |                                                                                      |  |  |

| 400   | Input Chip control            | 0 : Reset input FIFOs                                                                |  |  |

|       |                               | 1 : Count Enable. 1 = Enable Time stamp counter.                                     |  |  |

|       |                               | 2 : SYNC error reset.                                                                |  |  |

|       |                               | 3 : SYNC to Error (STARY) connect.                                                   |  |  |

|       |                               | 4 : No effect, but registered.                                                       |  |  |

|       |                               | 5 : Run Enable. 1 = Enable input of SYNC, and Data to the                            |  |  |

|       |                               | FIFOS.                                                                               |  |  |

|       |                               | $6 \Rightarrow 15$ : registered data, but no action.                                 |  |  |

|       |                               | $16 \Rightarrow 31$ : always return 0.                                               |  |  |

| 404   | Input Status                  | Timestamp errors and others (NYI !!! )                                               |  |  |

| FUF   | input Status                  |                                                                                      |  |  |

| 500   | Time FIFO LS                  | $0 \Rightarrow 31$ : Time stamp bits $0 \Rightarrow 31$ .                            |  |  |

| 504   | Time FIFO MS                  | 0 => 15 : Timestamp bits $32 => 47$ .                                                |  |  |

|       |                               | 16 => 31 : 0.                                                                        |  |  |

| 508   | Time FIFO word                | $0 \Rightarrow 8$ : Number of words in the Timestamp FIFO                            |  |  |

|       | count                         |                                                                                      |  |  |

| 50C   |                               |                                                                                      |  |  |

| 510   | Group A fifo data             | 0 => 15 : Group A Pattern<br>16 => 31 : 0                                            |  |  |

| 514   |                               |                                                                                      |  |  |

| 518   | Group A fifo word             | $0 \Rightarrow 8$ : Number of words in the Group A FIFO                              |  |  |

| • • • | count                         | $16 \Rightarrow 31:0$                                                                |  |  |

| 51C   |                               |                                                                                      |  |  |

| 520   | Group B fifo data             | $0 \Rightarrow 15$ : Group B Pattern                                                 |  |  |

|       | 1                             | 16 => 31 : 0                                                                         |  |  |

| 524   |                               |                                                                                      |  |  |

| 528   | Group B fifo word             | $0 \Rightarrow 8$ : Number of words in the Group B FIFO                              |  |  |

|       | count                         | 16 => 31 : 0                                                                         |  |  |

| 52C   |                               |                                                                                      |  |  |

| 530   | Type fifo data                | 0 => 7 : Event type data.<br>8 => 31 : 0.                                            |  |  |

| 534   |                               | 0 < 51.0.                                                                            |  |  |

| 538   | Type fifo word                | $0 \Rightarrow 8$ : Number of words in the Event type FIFO                           |  |  |

| 330   | count                         | $16 \Rightarrow 31:0$                                                                |  |  |

| 53C   |                               |                                                                                      |  |  |

| 540   | Group A Ident                 | $0 \Rightarrow 31$ : Ident for Group A pattern.                                      |  |  |

| 544   | Group B Ident                 | $0 \Rightarrow 31$ : Ident for Group B pattern.                                      |  |  |

| 548   | SYNC Ident                    | $0 \Rightarrow 31$ : Ident for SYNC.                                                 |  |  |

| 54C   | Pause Ident                   | $0 \Rightarrow 31$ : Ident for STIVE.                                                |  |  |

| 550   | Resume Ident                  | $0 \Rightarrow 31$ : Ident for Pause.                                                |  |  |

| 554   | Undefined Ident               | $0 \Rightarrow 31$ : Ident for Kesuffe.<br>$0 \Rightarrow 31$ : Ident for Undefined. |  |  |

| 554   | 0 = -31. Ident 101 Ondernied. |                                                                                      |  |  |

| 558        | Write to FIFO.                | $0 \Rightarrow 31$ : write to FIFO.                                                                                                                                                                                                                                                                                                          |

|------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55C        |                               |                                                                                                                                                                                                                                                                                                                                              |

| 560        | FIFO flags                    | <ul> <li>0 : Group A FIFO empty</li> <li>1 : Group A FIFO full</li> <li>2 : Group B FIFO empty</li> <li>3 : Group B FIFO full</li> <li>4 : Control FIFO empty</li> <li>5 : Control FIFO full.</li> <li>6 : Timestamp FIFO full.</li> <li>6 : External FIFO almost full.</li> <li>9 : External FIFO full.</li> <li>10 =&gt; 31 : 0</li> </ul> |

| 600<br>700 | Load Timestamp Spare bus read | <ul> <li>Load a new value into the Timestamp counter for loading at a re-sync SYNC pulse.</li> <li>0 =&gt; 31 : Data for new Timestamp 16 =&gt; 47 value.</li> <li>A write to this register sets the Re_SYNC enable.</li> <li>0 =&gt; 31 : Input chip end of Spare connections between the two Alteras.</li> </ul>                           |

# Appendix F. Logic Inspection Line signal selection.

Logic Inspection Line Signal selection. This inform ation is provided for completeness, it is not intended for a us er to need to vie w the m ajority of thes e signals.

| Code     | Signal Name    | Description                                      |

|----------|----------------|--------------------------------------------------|

| 0 => 1F  | Disconnected   | Allows other units to drive the line.            |

| 20 => 2F | Group A inputs | Input monitors for Group A.                      |

|          | 0 => 15        |                                                  |

| 30 => 3F | Group B inputs | Input monitors for Group B.                      |

|          | 0 => 15        |                                                  |

| 40       | Group B Hit    | Group B Pattern hit.                             |

| 41       | Group B End    | Group B Gated mode End signal                    |

| 42       | Gate A         | Group A Gate input.                              |

| 43       | Gate B         | Group B Gate input.                              |

| 44       | Sync pulse     | Sync detected 10nS pulse                         |

| 45       | Sync error     | Sync error flag                                  |

| 46       | Aneb           | Output of Timestamp sync comparator              |

| 47       | Re-load window | Window a fter S YNC pulse during which a re-load |

|          |                | can occur.                                       |

| 48       | Load stamp     | Re-load pu lse. Loads the new value into the     |

|          |                | Timestamp counter                                |

| 49       | Load Enable    | Indicates a re-load has been programmed.         |

| 4A       | Time FIFO read | FIFO read request signal for the Timestamp FIFO  |

| 4B       | Time FIFO full | Flag                                             |

| 4C       | Time FIFO      | Flag                                             |

|          | empty          |                                                  |

| 4D       | Group A FIFO   | FIFO read request signal for the Group A FIFO    |

|          | read           |                                                  |

| 4E       | Group A FIFO   | Flag                                             |

|          | full            |                                                       |

|----------|-----------------|-------------------------------------------------------|

| 4F       | Group A FIFO    | Flag                                                  |

|          | empty           |                                                       |

| 50       | Group B FIFO    | FIFO read request signal for the Group B FIFO         |

|          | read            |                                                       |

| 51       | Group B FIFO    | Flag                                                  |

|          | full            |                                                       |

| 52       | Group B FIFO    | Flag                                                  |

|          | empty           |                                                       |

| 53       | Time FIFO       | FIFO write request for the Timestamp FIFO             |

|          | write           |                                                       |

| 54       | Group A FIFO    | FIFO write request for the Group A FIFO               |

|          | write           |                                                       |

| 55       | Group B FIFO    | FIFO write request for the Group B FIFO               |

|          | write           |                                                       |

| 56       | Pause           | Pause signal                                          |

| 57       | Resume          | Resume signal                                         |

| 58       | Type FIFO read  | FIFO read request signal for the Type FIFO            |

| 59       | Type FIFO full  | Flag                                                  |

| 5A       | Type FIFO       | Flag                                                  |

|          | empty           |                                                       |

| 5B       | SYNC            | SYNC pulse from the Metronome                         |

| 5C       | STARX           | STARX (Reset) from the Metronome                      |

| 5D       | Out of step     | Internal FIFOs are out of step ??????                 |

| 5E       | Ext FIFO write  | FIFO Write clock to the external FIFO                 |

|          | clock           |                                                       |

| 5F       | Ext FIFO write  | FIFO Write request to the external FIFO               |

| 60       | Ext FIFO almost | Flag ( active low )                                   |

|          | full            |                                                       |

| 61       | Ext FIFO full   | Flag ( active low )                                   |

| 62       | Group A Hit     | Group A Pattern hit.                                  |

| 63       | Group A End     | Group A Gated mode End signal                         |

| 70 => 7F | Group A         | The Stretched inputs for Group A.                     |

|          | stretched 0 =>  |                                                       |

| 0.0      | 15              |                                                       |

| 80       | Loadreg         | Load signal, enables reg isters when selected to load |

| 01       | China 1 t       | data                                                  |

| 81       | Chip select     | Active to select vme access to the input chip         |

| 82       | Asn             | VME address strobe                                    |

| 83       | DS0n            | VME Data strobe 0                                     |

| 84       | DS1n            | VME Data strobe 1                                     |

| 85       |                 | VME data asknowladza                                  |

| 86       | DTACK           | VME data acknowledge                                  |

| 87       | STARX           | VME Interment color cycle dec cycle : 1t:for          |

| 88       | Iackn           | VME Interrupt acknowledge cycle identifier            |

| 89       | Irq1            | Interrupt line                                        |

| 8a<br>8b | Irq2            | Interrupt line                                        |

| 8b       | Irq3            | Interrupt line                                        |

| 8c       | Irq4            | Interrupt line                                        |

| 8d      | Irq5        | Interrupt line                                |

|---------|-------------|-----------------------------------------------|

| 8e      | Irq6        | Interrupt line                                |

| 8f      | Irq7        | Interrupt line                                |

| 90      | Iackinn     | Interrupt cycle chain token in                |

| 91      | Iackoutn    | Interrupt cycle chain token out               |

| 92      | Sharc clock | SHARC bus clock pulses.                       |

| 93      | Sharc ack   | SHARC bus acknowledge                         |

| 94      | Sharc data0 | SHARC data bit                                |

| 95      | Sharc data1 |                                               |

| 96      | Sharc data2 |                                               |

| 97      | Sharc data3 |                                               |

| 98 – 9f | NYI         |                                               |

| A0      | Fifo pafn   | FIFO programmable almost full                 |

| A1      | Fifo paen   | FIFO programmable almost empty                |

| A2      | Fifo hfn    | FIFO Half empty                               |

| A3      | Fifo ffn    | FIFO full                                     |

| A4      | Fifo efn    | FIFO empty                                    |

| A5      | Fifo erclk  | Fifo erclk ?????                              |

| A6      | Fifo erenn  | Fifo erenn ????                               |

| A7      | Fifo rclk   | Fifo read clock                               |

| A8      | Fifo rcsn   | Fifo read chip select                         |

| A9      | Fifo renn   | Fifo read enable                              |

| Aa      | Fifo oen    | Fifo output enable                            |

| Ab      | Fifo prsn   | Fifo partial reset                            |

| Ac      | Fifo mrsn   | Fifo master reset                             |

| Ad      | Fifo ready  | Fifo data has been read, and is ready for use |

| Ae      | Fifo rdreq  | Request from sharc software for a fifo read   |

| Af      | Vme req     | Request from vme for a read of fifo data      |

| B0      | Lost track  | Output of the track comparison system ?       |